一般情況下,當設計普通單、雙面板時,無需考慮PCB的疊層問題,通常直接選擇銅厚和板厚符合設計要求的覆銅板直接加工。但設計4層以上的PCB時,疊層設計直接影響PCB的性能和價格。

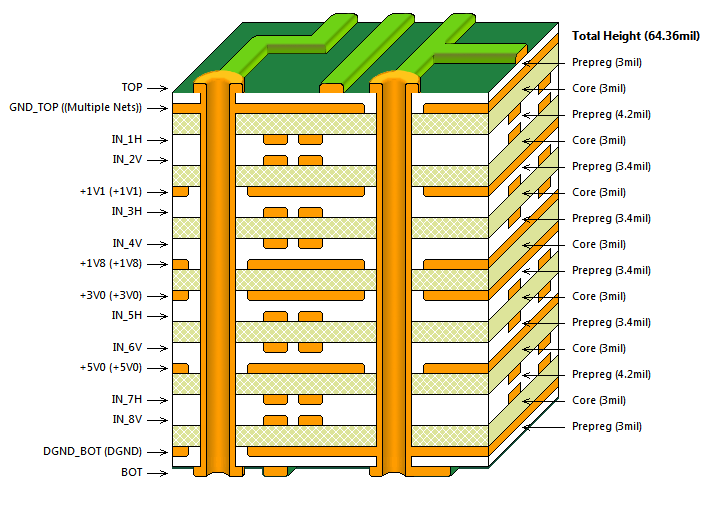

16層板的疊層設計

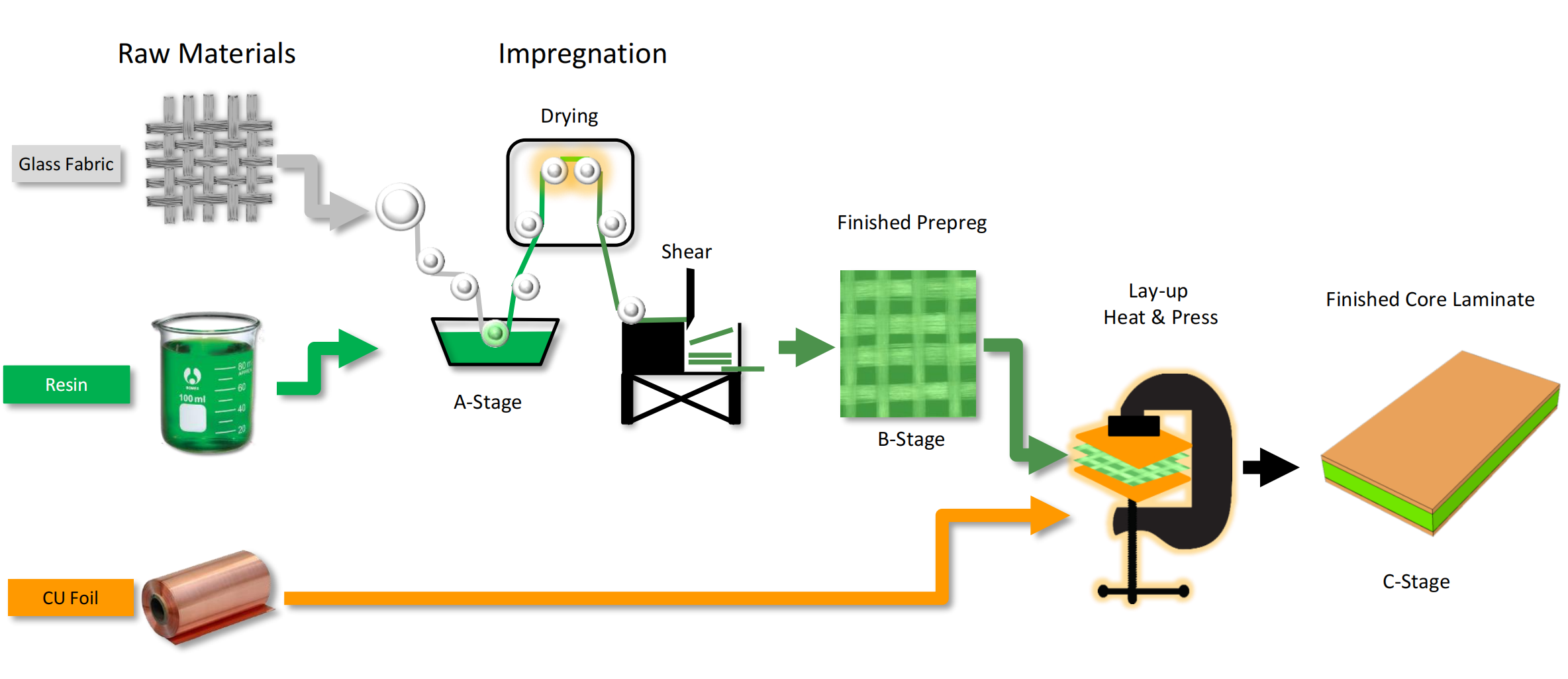

多層PCB由覆銅芯板(Core)、半固化片(prepreg,簡稱PP)與銅箔,一起按照疊層設計組合,經過壓合制成。

在PCB開始設計之前,Layout工程師會根據電路板的尺寸、電路的規模和電磁兼容(EMC)的要求確定PCB的層數,然后確定元器件的布局,最后確認信號層、電源層和地層的劃分。

PCB疊層需要從層數、信號類型、板厚、材料選擇、銅厚、阻抗控制、EMI/EMC屏蔽、熱管理、成本和可測試性等多方面考慮。

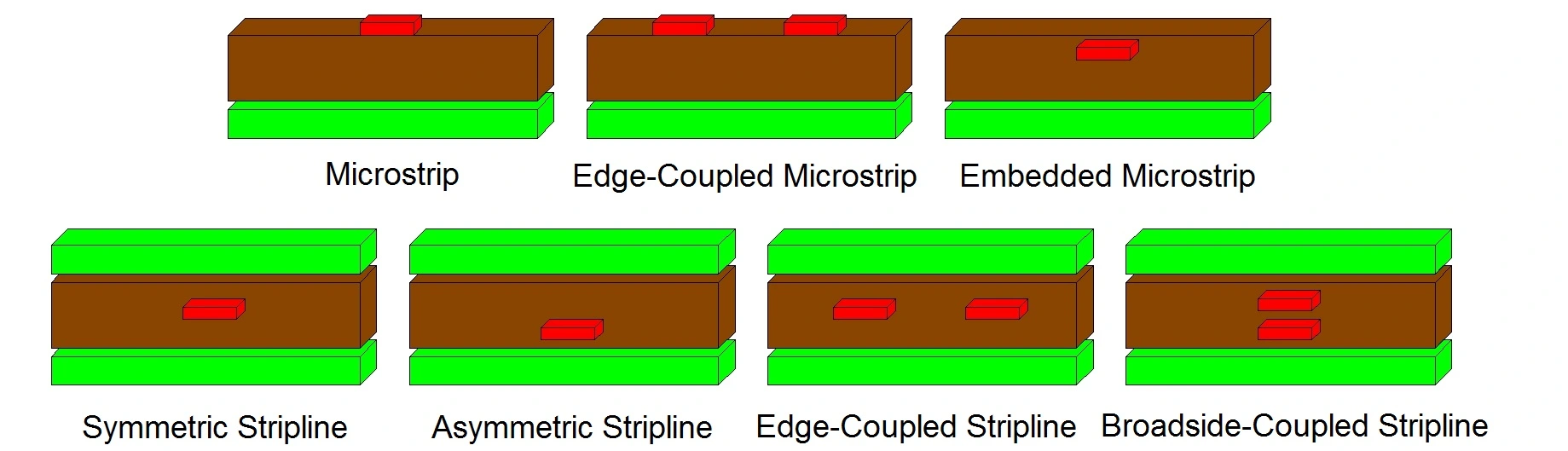

對于關鍵信號線,需要構建GND/Signal/GND的疊層組合,相鄰信號層的帶狀線,交叉垂直布線,以最小化串擾耦合。從信號完整性的角度來講,關鍵高速信號使用帶狀線(Stripline)布線,非關鍵高速信號可以選擇使用微帶線(Microstrip)布線。

如非必要,不建議使用寬邊耦合帶狀線(Broadside-Coupled Stripline ),PCB加工過程中的曝光和蝕刻的偏移都會造成重疊錯位,加工過程困難而且難以保證阻抗的一致性。

微帶線和帶狀線布線的類型

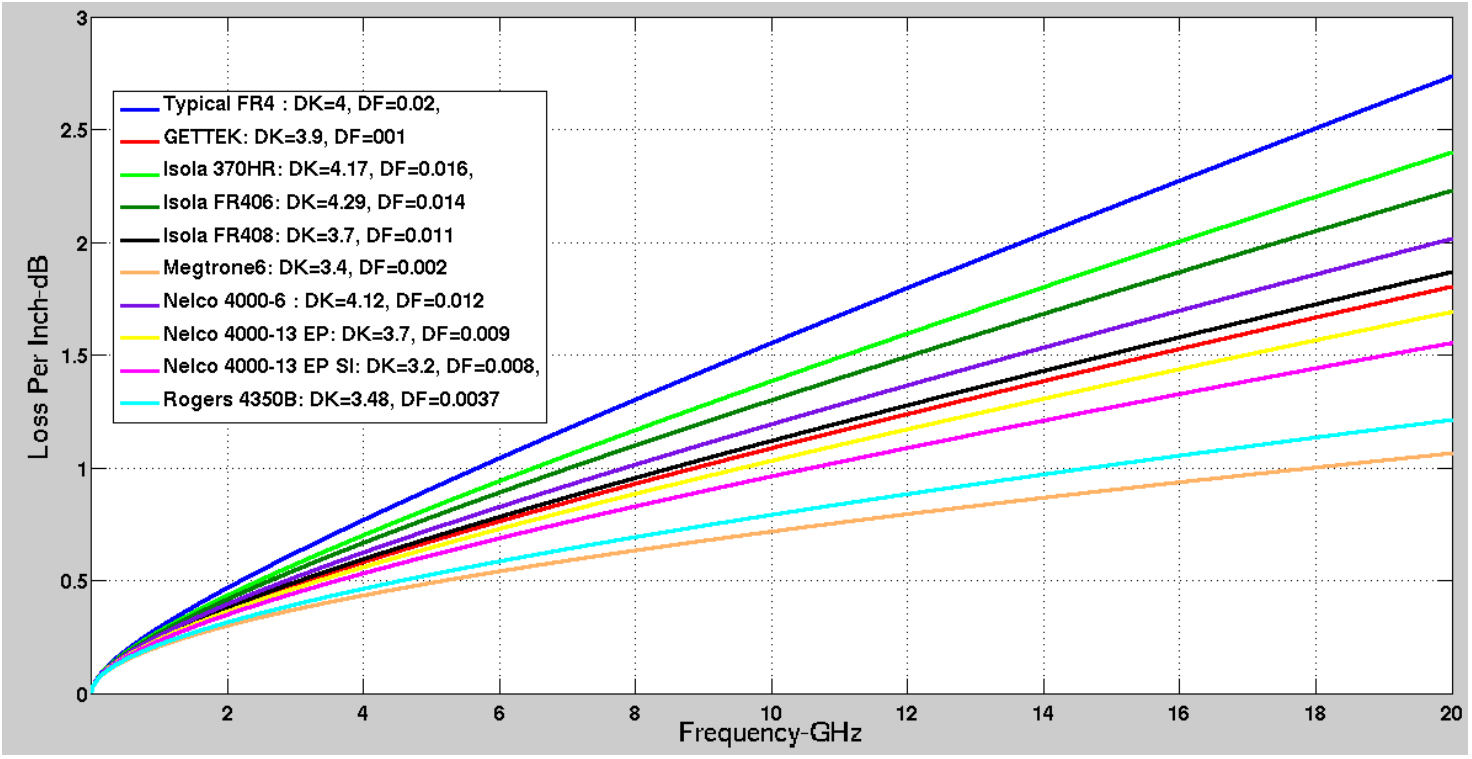

FR-4能夠滿足大多數PCB的需求,價格便宜而且電氣性能良好,高速PCB會選用高速板材,比如松下的Megtron4/6等,射頻PCB會選用 碳氫、Teflon或者陶瓷基板。如汽車燈板等對散熱要求高的設計場景,會選用鋁基或者銅基板材,在Mini LED等顯示場景會使用玻璃基板材。

板材的關鍵性能指標如下:

高速PCB需要選擇具有最低損耗角正切和較小介電常數的介電材料,高速PCB的設計需要特別注意材料明細,包括玻璃纖維(Fiberglass),電介質矩陣(Dielectric Matrix)和銅(Copper)。在較高數據速率下的信號具有較高的頻率單元,波長更短,阻抗不連續會產生更多反射。需要考慮玻纖效應和銅箔表面粗糙度的影響。

不同型號板材對信號的衰減

在上圖中,Typical FR4在28Gbps時每英寸有近2dB平均損耗(Nyquist為14GHz),Megtron6在相同頻率只有0.85dB。

不同的玻纖對應的編織粗細不一樣,開窗和交織的厚度也不一樣,如果信號分別布在開窗上和玻纖上所表現的特性(阻抗、時延、損耗)也不一樣(開窗和玻纖Dk/Df特性不一樣導致的),這就是玻纖效應。

芯板(Core)的制造過程

玻纖布的類型

緩解玻纖效應的方法:

擇最小化樹脂窗口的玻纖類型材料;

使用Zig-Zag等10°走線方法;

在制板的時候讓板廠旋轉一定的角度;

使用扁平開纖玻布或者平織布。

銅箔粗糙度(銅牙)使線路的寬度、線間距不均勻,從而導致阻抗不可控,同時由于趨膚效應,電流集中在導體的表層,銅箔的表面粗糙度影響信號傳輸的長度。

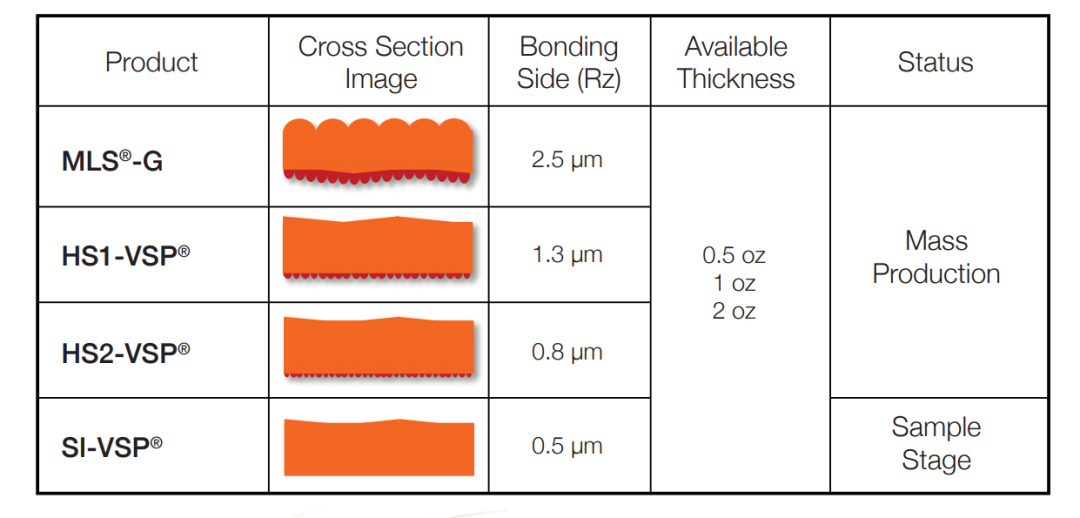

不同等級銅箔的表面粗糙度

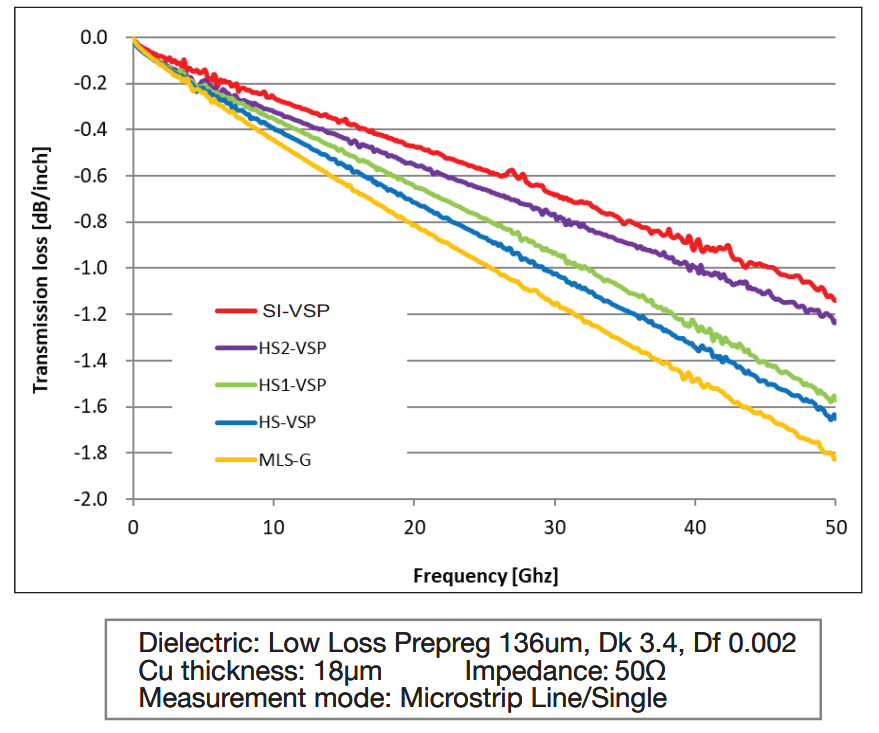

如下圖所示,在5GHz以下銅箔粗糙度的影響不是太明顯,大于5GHz銅箔粗糙度的影響開始越來越大,在大于10Ghz的高速信號的設計時尤其需要重視。

銅箔粗糙度對高速信號的衰減

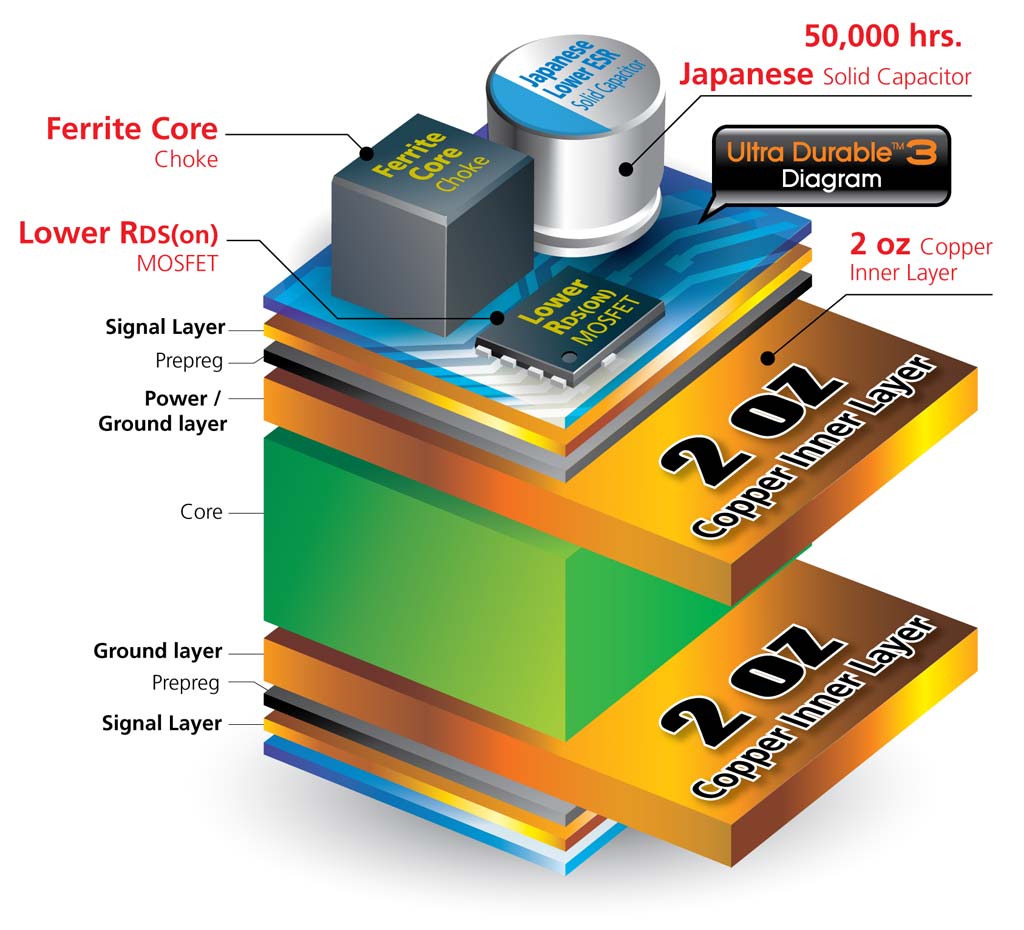

PCB銅箔的厚度以盎司(oz)為單位。常見的銅厚有三個尺寸,0.5oz(內層)、1oz(表層)和2oz,主要用在消費和通訊類產品上。3oz以上屬于厚銅,常用于高壓、大電流的電力電子產品。

電源板的疊層設計

疊層設計時必須平衡銅箔的厚度,使電源/地平面層銅的厚度滿足載流要求。對于信號層銅的厚度來講,線寬/線距較小,需要銅盡可能薄才能滿足精確的蝕刻的要求。高速信號線由于趨膚效應的影響,電流只在銅箔表面附近流動,更厚的銅箔并不會帶來更好的性能。所以內層信號層的銅厚通常為Hoz,即0.5盎司。

PCB上很多接口信號線都有阻抗要求,常見的單端50Ω、差分100Ω等。阻抗控制,需要有參考平面,一般需要四層以上。

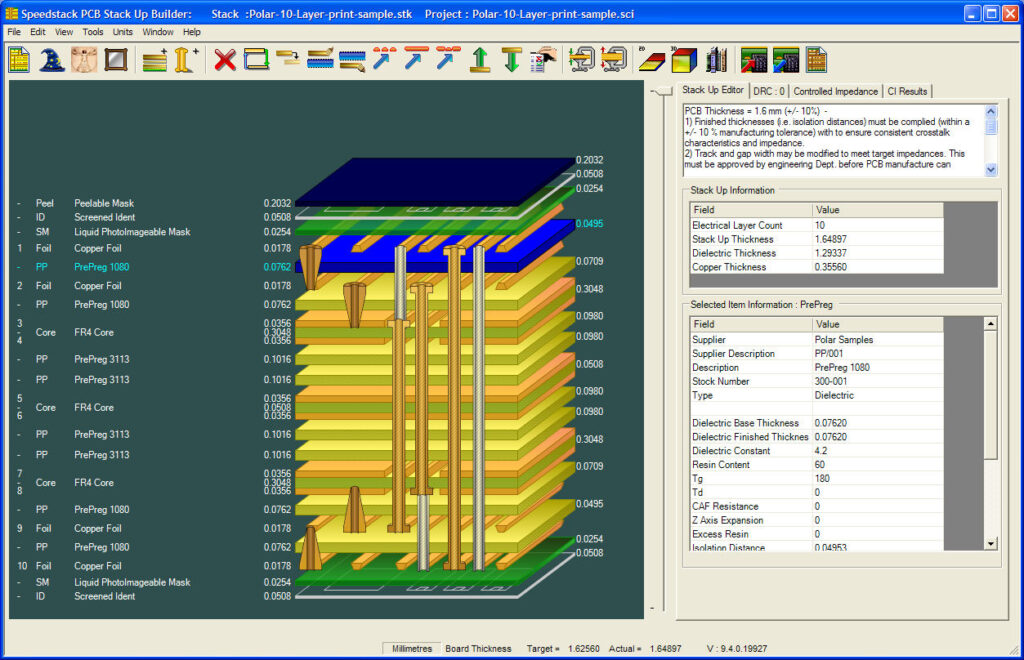

阻抗不匹配會導致信號失真、反射和輻射等信號完整性問題,影響PCB的性能。走線的銅厚、介電常數、線寬、線距都會影響阻抗。我們可以根據各種EDA工具去計算阻抗,然后按照設計的疊層結構,去調整走線的參數。目前常規的板廠都可以把阻抗控制在10%。

使用Polar來計算疊層阻抗

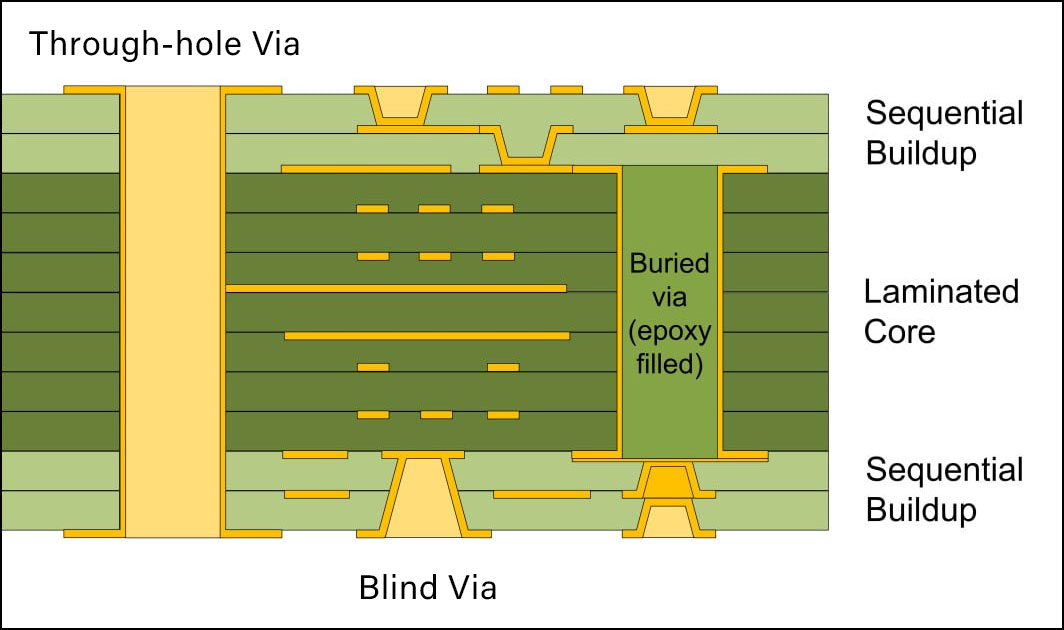

PCB中孔的類型

通孔(PTH)貫穿整個PCB可以連接所有層。盲孔(Blind Via)可以將外層連接至一個或多個內層,但不穿過PCB。埋孔(Buried Via)只連接PCB的內層。

高密度(HDI)PCB經常會使用盲孔和埋孔來優化布線空間,盲孔和埋孔也造成了PCB需要多次壓合增加了工序,PCB的制造難度上升,因此也更加昂貴。

在疊層設計時,需要根據設計需要來設計整板的孔結構,在滿足設計的前提下,盡量簡化孔的結構。

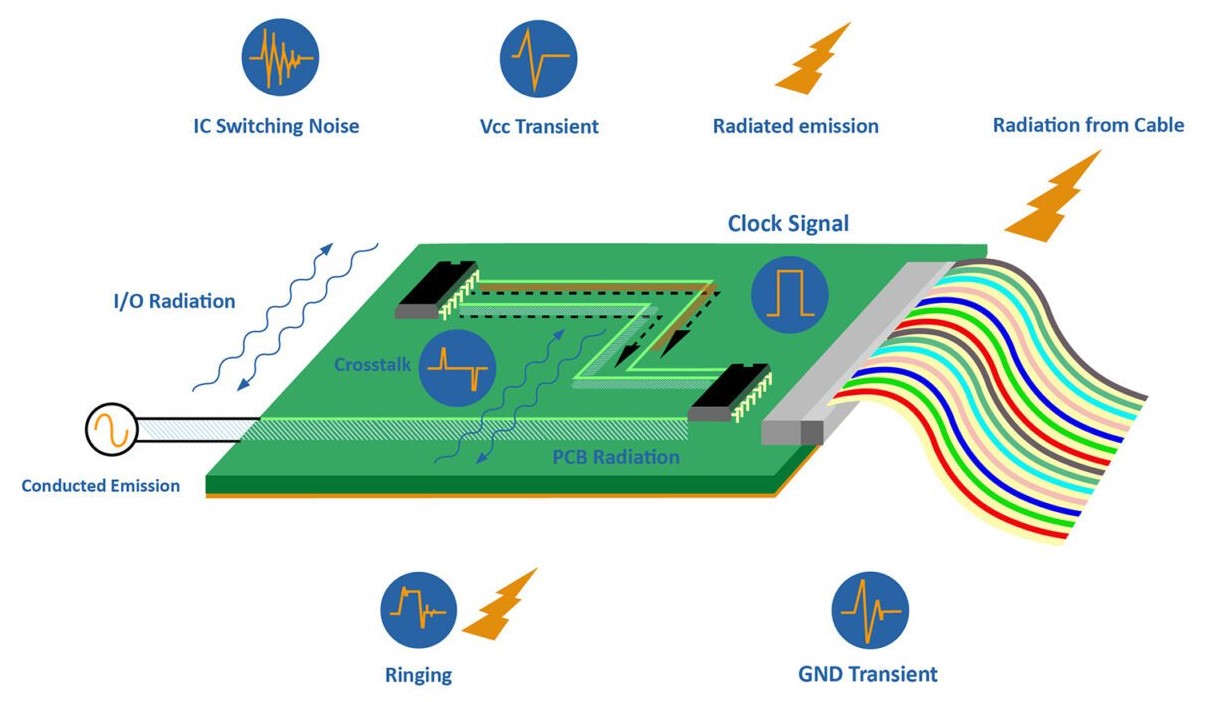

PCB疊層EMC設計時遵循以下原則:

板內電源平面和地平面盡量相互鄰近,一般地平面在電源平面之上,這樣的設計可以有效利用層間電容作為電源的平滑電容,同時接地平面對電源平面分布的輻射電流起到屏蔽作用。

電源和地層分配在內層,地平面可視為屏蔽層,可以很好地抑制電路板上固有的共模RF干擾,減小高頻電源的分布阻抗。

布線層應盡量安排與電源或地平面相鄰以產生通量對消作用。

PCB板上的輻射

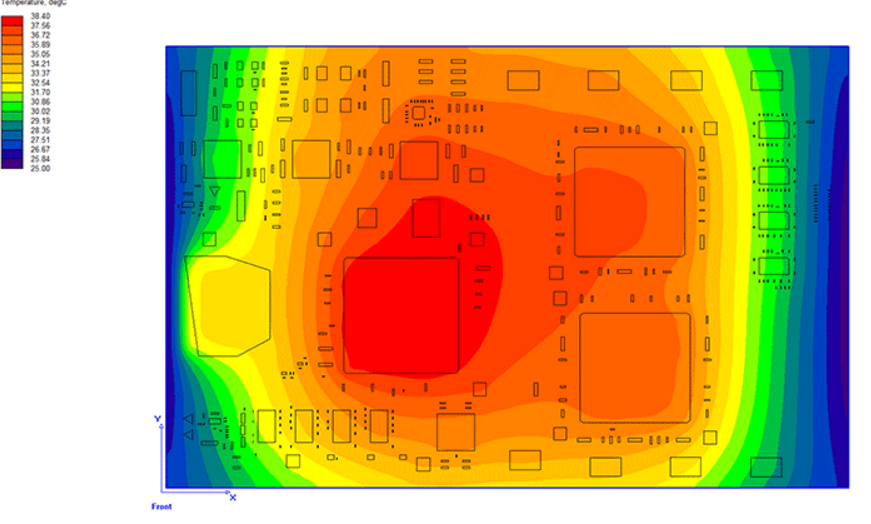

PCB疊層設計需要考慮熱管理,保證元器件散發的熱量有效傳導出去,防止熱損壞提高電路可靠性。在設計流程中,我們會先根據元器件功耗進行熱仿真,根據仿真結果優化元器件布局和設計相應的散熱方案。

在疊層設計階段,也可以針對性做散熱設計:

優先選擇導熱系數高的板材,按需選擇金屬基板;

大功率器件下方設計散熱焊盤,使用散熱孔;

埋銅塊,嵌銅柱,提高熱傳導效率;

增加地平面,空白區域鋪地,增大散熱面積。

板級熱仿真

常規的PCB成品厚度為0.5mm、0.8mm、1.0mm、1.2mm、1.6mm、2.0mm、3.2mm、6.4mm等等。一般面積小的板厚相對較薄,經常插拔、安裝應力較大、面積大的板子,從結構可靠性角度需要做厚一些。

PCB疊層設計一般遵循以下步驟:

1.確定層疊的總厚度,即板厚;

2.確定PCB層數,并分配信號層、地平面層和電源層;

3.確定內層和外層的銅厚;

4.確定阻抗線的分布;

5.確定過孔結構;

6.確定每層的殘銅率,最好要對稱;

7.選擇滿足設計要求的板材、PP和銅箔材料。

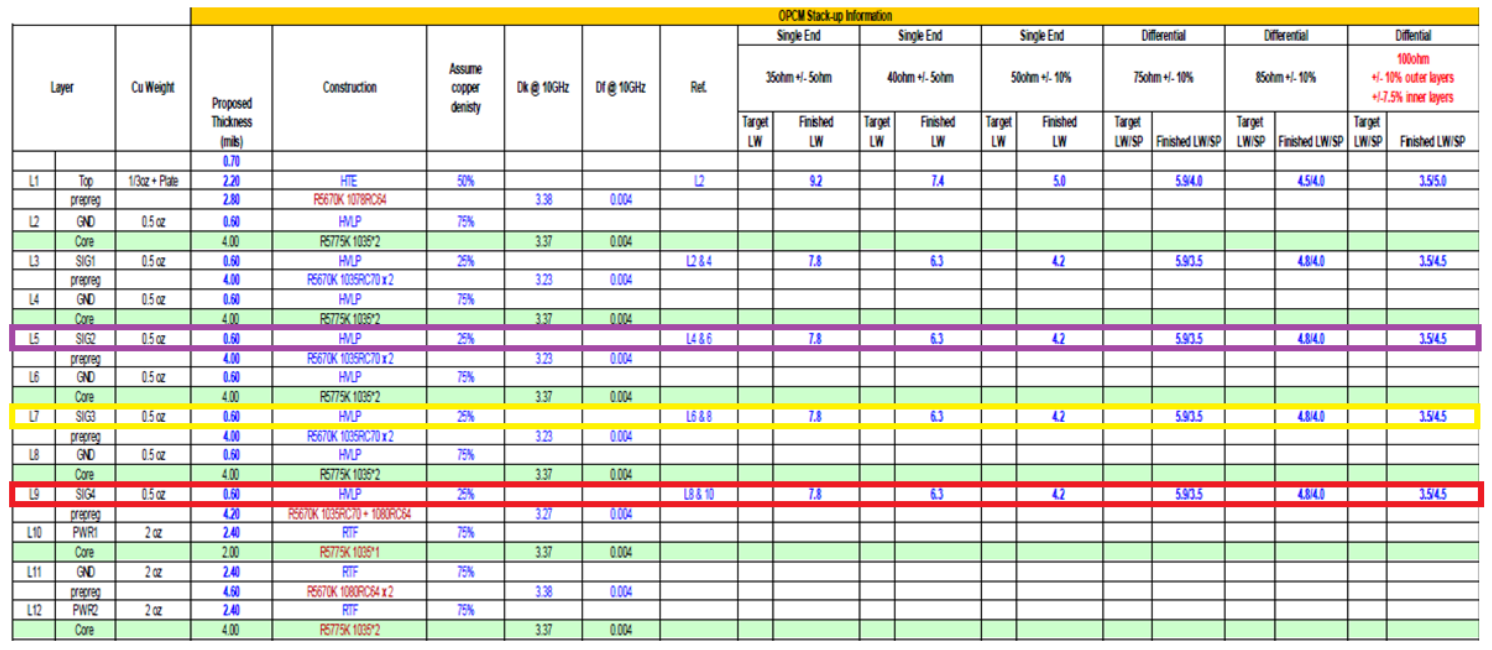

以12層板為例,設計好的疊層結構如下:

聲明:文章內容整理自網絡公開素材, 版權歸原作者平臺所有,僅用于信息分享,如有侵權請聯系刪除。